商機詳情 -

廣東HDIPCB打樣

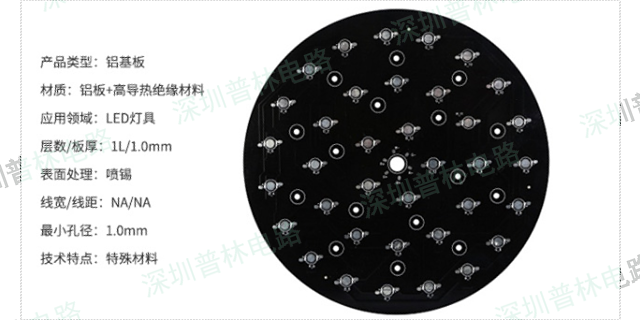

普林電路在中PCB制造過程中,注重對環保要求的滿足。隨著環保意識的不斷提高,PCB生產企業需要采取環保措施。普林電路在生產過程中采用了環保型的原材料和生產工藝,減少對環境的污染。例如,在蝕刻工序中,采用先進的蝕刻液回收系統,對蝕刻液進行循環利用,降低蝕刻液的消耗和廢棄物的排放。在產品包裝方面,選用可回收、可降解的包裝材料,減少包裝廢棄物對環境的影響,體現了企業的社會責任。對于中小批量訂單的生產,普林電路擁有完善的成本控制體系。合理控制成本是企業在市場競爭中的重要手段。普林電路通過優化生產流程、提高原材料利用率、降低設備能耗等方式,有效降低生產成本。在原材料采購環節,通過與供應商的談判和集中采購等方式,獲取更優惠的價格。在生產過程中,通過精細化管理,減少生產過程中的浪費,提高生產效率,從而在保證產品質量的前提下,為客戶提供具有競爭力的價格。高頻PCB憑借杰出的導電性和抗干擾能力,應用于雷達、通信系統等高要求領域,提供高速、低損耗的信號傳輸。廣東HDIPCB打樣

PCB 的品質管控是深圳普林電路的生命線,依托完善體系確保產品可靠性。PCB 的品質直接影響終端設備的性能與壽命。深圳普林電路建立了嚴格的質量管理體系,遵循 ISO 9001標準,從制前評估、標準下發到過程管控、異常分析,形成全流程閉環管理。通過 X-RAY、AOI、阻抗測試等先進檢測設備,對來料、制程、成品進行多層級檢驗,確保產品一次性準交付率達 95%。同時,引入 EMS 系統實現生產數據實時監控,通過持續優化流程,將隱性操作標準化,有效降低缺陷率,保障每一塊 PCB 的品質。深圳階梯板PCB生產廠家通過精密的過孔填充和鍍銅技術,普林電路確保信號傳輸的低損耗和高速度,滿足5G通信設備的苛刻要求。

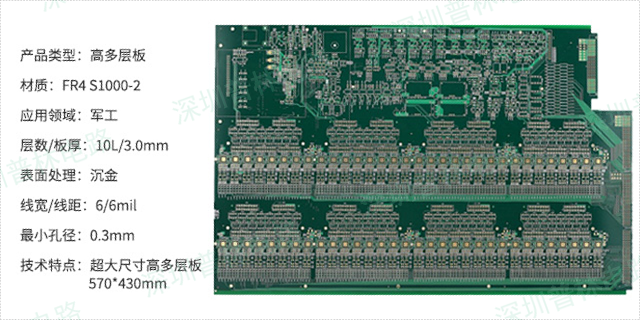

PCB 的小線寬 / 線距能力標志著制造精度,深圳普林電路在高頻板中實現 3mil/3mil(0.076mm/0.076mm)的突破。PCB 的細線路加工采用激光直接成像(LDI)技術,分辨率達 50μm,配合化學蝕刻均勻性控制(側蝕量<10%),在羅杰斯板材上實現 3mil 線寬的穩定生產。為某 5G 基站廠商定制的 20 層高頻板,線寬公差 ±0.01mm,阻抗匹配精度 ±5%,支持 28GHz 頻段信號傳輸,插入損耗<0.8dB/in。該技術突破使 PCB 在有限面積內集成更多射頻鏈路,助力小型化基站設計,較傳統方案節省 40% 的空間占用。

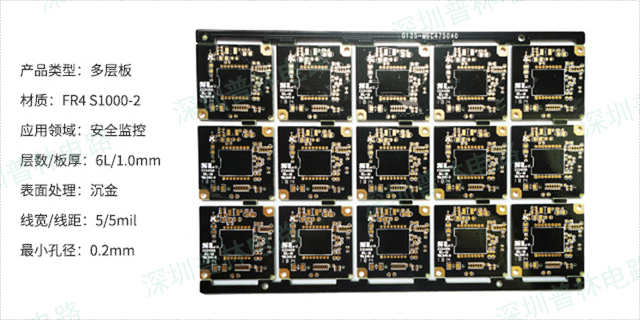

PCB 的階梯槽工藝通過數控銑削實現基板分層結構,深圳普林電路控制精度達 ±0.02mm,滿足復雜結構需求。PCB 的階梯槽工藝可根據設計要求銑削出多層階梯狀結構,深圳普林電路為某工業控制設備生產的 8 層 PCB,采用 3 階階梯槽設計,每層深度分別為 0.5mm、1.0mm、1.5mm,槽壁垂直度≥89°,表面粗糙度 Ra≤3.2μm。此類結構可嵌入不同厚度的屏蔽罩或散熱片,實現電路模塊的物理隔離與高效散熱。在安防攝像頭主板中,階梯槽區域用于安裝圖像傳感器芯片,通過金屬包邊工藝提升 EMC 性能,使抗干擾能力提升 20dB,滿足戶外復雜電磁環境下的穩定工作需求。PCB工業控制板強化三防處理,鹽霧測試達96小時無腐蝕。

普林電路在研發樣品的PCB制造中,注重知識產權保護。PCB知識產權知識強調了保護客戶知識產權的重要性。普林電路與客戶簽訂嚴格的保密協議,對客戶的設計圖紙、技術方案等信息進行嚴格保密。在生產過程中,采取有效的措施防止信息泄露,確保客戶的知識產權得到充分保護,讓客戶能夠放心地將研發樣品的制造任務交給普林電路。在中PCB生產制造過程中,普林電路積極開展技術創新活動。技術創新是企業保持競爭力的關鍵。普林電路投入大量資金用于研發,鼓勵技術人員開展技術創新項目。例如,在新型材料應用方面進行研究,探索使用性能更優異的新型覆銅板,以提高PCB的性能和可靠性。通過技術創新,普林電路不斷提升自身的技術水平和產品質量,在市場競爭中占據優勢地位。深圳普林電路制造的高頻PCB注重電磁兼容性,能夠有效減少干擾,提升通信設備的信號傳輸質量。廣東HDIPCB打樣

PCB設計評審服務提前規避23類常見EMC/EMI問題。廣東HDIPCB打樣

面向醫療設備制造商,深圳普林電路建立符合ISO13485標準的質控體系,重點管控生物兼容性材料的選用(如符合USPClassVI標準的基材)及可追溯性管理。在PCB制造中采用無鉛表面處理工藝,避免ROHS禁用物質殘留;通過微切片分析確保孔壁銅厚≥25μm,滿足高頻電刀等設備的電流承載需求。PCBA階段執行潔凈室組裝,對清洗劑殘留量進行離子色譜檢測(<1.56μg/cm2),并建立滅菌驗證數據庫(環氧乙烷、伽馬射線等)。面向智能穿戴、傳感器節點等物聯網終端,普林電路開發出超小型PCB集成方案。采用HDI(高密度互連)技術實現1階激光盲孔(孔徑75μm)與3+4+3疊層結構,在20×15mm面積內集成藍牙模組、MCU及天線單元。應用半固化片流膠控制技術,將介質層厚度壓縮至25μm,線寬/線距降至40/40μm。針對紐扣電池供電場景,提供損耗設計方案(損耗角正切≤0.002@1GHz),延長設備續航時間。廣東HDIPCB打樣