商機(jī)詳情 -

鄂州打造PCB制板

***,在完成PCB設(shè)計(jì)后,進(jìn)行生產(chǎn)與測試是不可或缺的重要步驟。生產(chǎn)過程中,設(shè)計(jì)師需要與制造商緊密合作,確保每一個(gè)細(xì)節(jié)都符合設(shè)計(jì)規(guī)格。在這一階段,任何一個(gè)微小的失誤都可能導(dǎo)致**終產(chǎn)品的故障。因此,耐心與細(xì)致是PCB設(shè)計(jì)師必須具備的品質(zhì)。而在測試環(huán)節(jié),設(shè)計(jì)師則需對電路進(jìn)行***的功能性和可靠性測試,確保其在實(shí)際應(yīng)用中的穩(wěn)定性與安全性。綜上所述,PCB設(shè)計(jì)不僅是一項(xiàng)技術(shù)活,更是一門藝術(shù)。它既需要嚴(yán)謹(jǐn)?shù)目茖W(xué)態(tài)度,又需富有創(chuàng)意的設(shè)計(jì)思維。隨著時(shí)代的進(jìn)步與新技術(shù)的不斷涌現(xiàn),PCB設(shè)計(jì)將迎來更廣闊的發(fā)展空間與應(yīng)用前景,也將為推動電子產(chǎn)品的創(chuàng)新與發(fā)展,提供更為堅(jiān)實(shí)的基礎(chǔ)。階梯槽孔板:深度公差±0.05mm,機(jī)械裝配嚴(yán)絲合縫。鄂州打造PCB制板

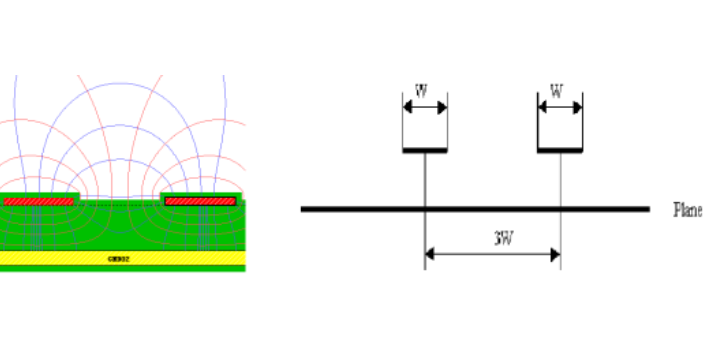

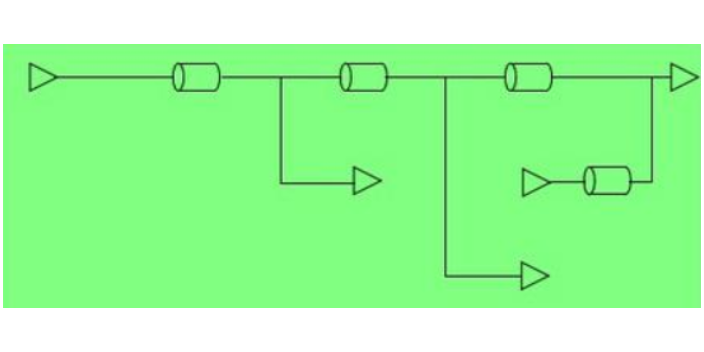

在高速數(shù)字系統(tǒng)中,由于脈沖上升/下降時(shí)間通常在10到幾百p秒,當(dāng)受到諸如內(nèi)連、傳輸時(shí)延和電源噪聲等因素的影響,從而造成脈沖信號失真的現(xiàn)象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,可能由于很小的差異導(dǎo)致高速系統(tǒng)設(shè)計(jì)的失敗;在電子產(chǎn)品向高密和高速電路設(shè)計(jì)方向發(fā)展,解決一系列信號完整性的問題,成為當(dāng)前每一個(gè)電子設(shè)計(jì)者所必須面對的問題。業(yè)界通常會采用在PCB制板前期,通過信號完整性分析工具盡可能將設(shè)計(jì)風(fēng)險(xiǎn)降,從而也促進(jìn)了EDA設(shè)計(jì)工具的發(fā)展……信號完整性(SignalIntegrity,簡稱SI)問題是指高速數(shù)字電路中,脈沖形狀畸變而引發(fā)的信號失真問題,通常由傳輸線阻抗不匹配產(chǎn)生的問題。而影響阻抗匹配的因素包括信號源的架構(gòu)、輸出阻抗(outputimpedance)、走線的特性阻抗、負(fù)載端的特性、走線的拓樸(topology)架構(gòu)等。解決的方式可以采用端接(termination)與調(diào)整走線拓樸的策略。信號完整性問題通常不是由某個(gè)單一因素導(dǎo)致的,而是板級設(shè)計(jì)中多種因素共同作用的結(jié)果。信號完整性問題主要表現(xiàn)形式包括信號反射、信號振鈴、地彈、串?dāng)_等;1,AltiumDesigner信號完整性分析(機(jī)理、模型、功能)在AltiumDesigner設(shè)計(jì)環(huán)境下。十堰高速PCB制板價(jià)格大全。這個(gè)過程如同藝術(shù)家在畫布上揮毫灑墨,雖然看似簡單,卻蘊(yùn)含著無盡的智慧與創(chuàng)意。

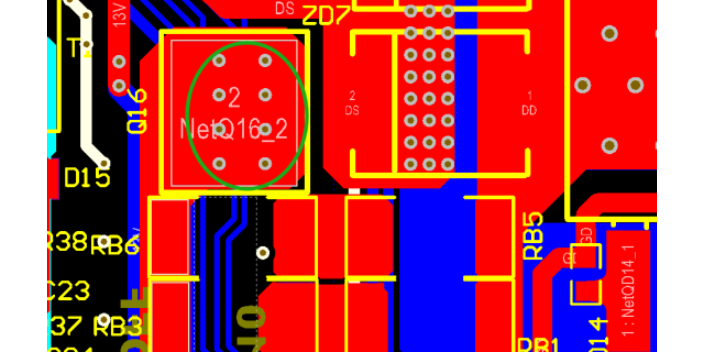

AltiumDesigner要求必須建立一個(gè)工程項(xiàng)目名稱。在原理圖SI分析中,系統(tǒng)將采用在SISetupOption對話框設(shè)置的傳輸線平均線長和特征阻抗值;仿真器也將直接采用規(guī)則設(shè)置中信號完整性規(guī)則約束,如激勵(lì)源和供電網(wǎng)絡(luò)等,同時(shí),允許用戶直接在原理圖編輯環(huán)境下放置PCBLayout圖標(biāo),直接對原理圖內(nèi)網(wǎng)絡(luò)定義規(guī)則約束。當(dāng)建立了必要的仿真模型后,在原理圖編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,運(yùn)行仿真。b.布線后(即PCB版圖設(shè)計(jì)階段)SI分析概述用戶如需對項(xiàng)目PCB版圖設(shè)計(jì)進(jìn)行SI仿真分析,AltiumDesigner要求必須在項(xiàng)目工程中建立相關(guān)的原理圖設(shè)計(jì)。此時(shí),當(dāng)用戶在任何一個(gè)原理圖文檔下運(yùn)行SI分析功能將與PCB版圖設(shè)計(jì)下允許SI分析功能得到相同的結(jié)果。當(dāng)建立了必要的仿真模型后,在PCB編輯環(huán)境的菜單中選擇Tools->SignalIntegrity命令,運(yùn)行仿真。4,操作實(shí)例:1)在AltiumDesigner的Protel設(shè)計(jì)環(huán)境下,選擇File\OpenProject,選擇安裝目錄下\Examples\ReferenceDesign\4PortSerialInterface\4PortSerial,進(jìn)入PCB編輯環(huán)境,如下圖1.圖1在PCB文件中進(jìn)行SI分析選擇Design/LayerStackManager…,配置好相應(yīng)的層后,選擇ImpedanceCalculation…。

Inner_1),GND(Inner_2),Siganl_2(Bottom)。(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。顯然,方案3電源層和地層缺乏有效的耦合,不應(yīng)該被采用。那么方案1和方案2應(yīng)該如何進(jìn)行選擇呢?一般情況下,設(shè)計(jì)人員都會選擇方案1作為4層板的結(jié)構(gòu)。選擇的原因并非方案2不可被采用,而是一般的PCB板都只在頂層放置元器件,所以采用方案1較為妥當(dāng)。但是當(dāng)在頂層和底層都需要放置元器件,而且內(nèi)部電源層和地層之間的介質(zhì)厚度較大,耦合不佳時(shí),就需要考慮哪一層布置的信號線較少。對于方案1而言,底層的信號線較少,可以采用大面積的銅膜來與POWER層耦合;反之,如果元器件主要布置在底層,則應(yīng)該選用方案2來制板。如果采用如圖11-1所示的層疊結(jié)構(gòu),那么電源層和地線層本身就已經(jīng)耦合,考慮對稱性的要求,一般采用方案1。6層板在完成4層板的層疊結(jié)構(gòu)分析后,下面通過一個(gè)6層板組合方式的例子來說明6層板層疊結(jié)構(gòu)的排列組合方式和方法。(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。方案1采用了4層信號層和2層內(nèi)部電源/接地層,具有較多的信號層。PCB 制版將面臨更多的機(jī)遇與挑戰(zhàn),需要不斷探索和應(yīng)用新的材料、工藝和技術(shù),以滿足日益增長的市場需求。

機(jī)器軌道夾板不緊導(dǎo)致貼片偏移;機(jī)器頭部晃動;紅膠特異性過強(qiáng);爐溫設(shè)置不當(dāng);銅鉑間距過大;MARK點(diǎn)誤照導(dǎo)致元悠揚(yáng)打偏四、缺件真空泵碳片不良真空不夠?qū)е氯奔晃锥氯蛭撞涣迹辉穸葴y試不當(dāng)或檢測器不良;貼片高度設(shè)置不當(dāng);吸咀吹氣過大或不吹氣;吸咀真空設(shè)定不當(dāng)(適用于MPA);異形元件貼片速度過快;頭部氣管破烈;氣閥密封環(huán)磨損;回焊爐軌道邊上有異物擦掉板上元件;五、錫珠回流焊預(yù)熱不足,升溫過快;紅膠經(jīng)冷藏,回溫不完全;紅膠吸濕造成噴濺(室內(nèi)濕度太重);PCB板中水分過多;加過量稀釋劑;網(wǎng)板開孔設(shè)計(jì)不當(dāng);錫粉顆粒不勻。六、偏移電路板上的定位基準(zhǔn)點(diǎn)不清晰;電路板上的定位基準(zhǔn)點(diǎn)與網(wǎng)板的基準(zhǔn)點(diǎn)沒有對正;電路板在印刷機(jī)內(nèi)的固定夾持松動,定位模具頂針不到位;印刷機(jī)的光學(xué)定位系統(tǒng)故障;焊錫膏漏印網(wǎng)板開孔與電路板的設(shè)計(jì)文件不符合。要改進(jìn)PCBA貼片的不良,還需在各個(gè)環(huán)節(jié)開展嚴(yán)格把關(guān),防止上一個(gè)工序的問題盡可能少的流到下一道工序。剛?cè)峤Y(jié)合板:動態(tài)彎折萬次無損傷,適應(yīng)可穿戴設(shè)備需求。湖北PCB制板銷售電話

BGA封裝適配:0.25mm焊盤間距,支持高密度芯片集成。鄂州打造PCB制板

***的PCB設(shè)計(jì)師需要***了解各種電子器件的特性和性能,根據(jù)實(shí)際需求選擇合適的元器件,并合理布局、連接電路,使得電子產(chǎn)品能夠穩(wěn)定、高效地工作。同時(shí),PCB設(shè)計(jì)師還必須注重電磁兼容性和散熱問題,以確保電子產(chǎn)品在長時(shí)間運(yùn)行過程中不會出現(xiàn)過熱或電磁干擾等問題。總之,PCB設(shè)計(jì)是電子產(chǎn)品設(shè)計(jì)中不可或缺的一環(huán),它的優(yōu)良與否直接影響著整個(gè)電子產(chǎn)品的品質(zhì)和性能。只有具備豐富的知識和經(jīng)驗(yàn),并融入創(chuàng)新思維和工藝技巧,才能設(shè)計(jì)出***的PCB電路板,為電子產(chǎn)品的發(fā)展貢獻(xiàn)力量。鄂州打造PCB制板