商機詳情 -

十堰了解PCB制板銷售

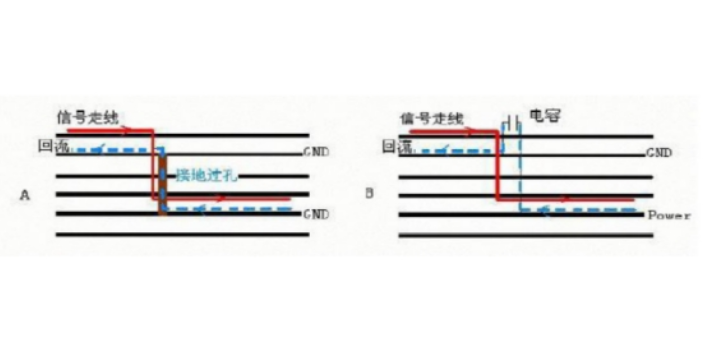

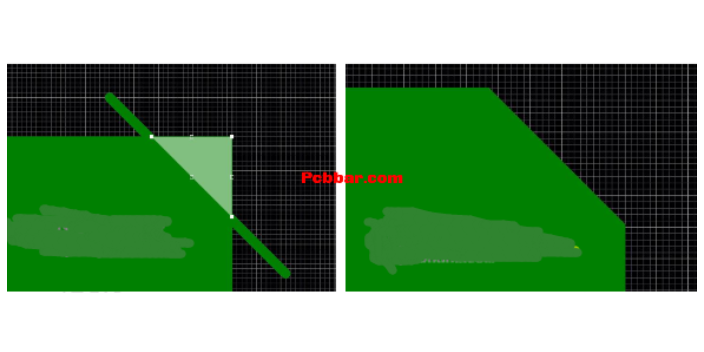

所有信號層盡可能與地平面相鄰;4、盡量避免兩信號層直接相鄰;相鄰的信號層之間容易引入串擾,從而導致電路功能失效。在兩信號層之間加入地平面可以有效地避免串擾。5、主電源盡可能與其對應地相鄰;6、兼顧層壓結構對稱。7、對于母板的層排布,現有母板很難控制平行長距離布線,對于板級工作頻率在50MHZ以上的(50MHZ以下的情況可參照,適當放寬),建議排布原則:元件面、焊接面為完整的地平面(屏蔽);無相鄰平行布線層;所有信號層盡可能與地平面相鄰;關鍵信號與地層相鄰,不跨分割區。注:具體PCB的層的設置時,要對以上原則進行靈活掌握,在領會以上原則的基礎上,根據實際單板的需求,如:是否需要一關鍵布線層、電源、地平面的分割情況等,確定層的排布,切忌生搬硬套,或摳住一點不放。8、多個接地的內電層可以有效地降低接地阻抗。例如,A信號層和B信號層采用各自單獨的地平面,可以有效地降低共模干擾。常用的層疊結構:4層板下面通過4層板的例子來說明如何各種層疊結構的排列組合方式。對于常用的4層板來說,有以下幾種層疊方式(從頂層到底層)。(1)Siganl_1(Top),GND(Inner_1),POWER(Inner_2),Siganl_2(Bottom)。(2)Siganl_1(Top),POWER。在現代電子技術的發展中,印刷電路板(PCB)制版無疑是一個至關重要的環節。十堰了解PCB制板銷售

布線前的阻抗特征計算和信號反射的信號完整性分析,用戶可以在原理圖環境下運行SI仿真功能,對電路潛在的信號完整性問題進行分析,如阻抗不匹配等因素的信號完整性分析是在布線后PCB版圖上完成的,它不僅能對傳輸線阻抗、信號反射和信號間串擾等多種設計中存在的信號完整性問題以圖形的方式進行分析,而且還能利用規則檢查發現信號完整性問題,同時,AltiumDesigner還提供一些有效的終端選項,來幫助您選擇解決方案。2,分析設置需求在PCB編輯環境下進行信號完整性分析。為了得到精確的結果,在運行信號完整性分析之前需要完成以下步驟:1、電路中需要至少一塊集成電路,因為集成電路的管腳可以作為激勵源輸出到被分析的網絡上。像電阻、電容、電感等被動元件,如果沒有源的驅動,是無法給出仿真結果的。2、針對每個元件的信號完整性模型必須正確。3、在規則中必須設定電源網絡和地網絡,具體操作見本文。4、設定激勵源。5、用于PCB的層堆棧必須設置正確,電源平面必須連續,分割電源平面將無法得到正確分析結果,另外,要正確設置所有層的厚度。3,操作流程a.布線前(即原理圖設計階段)SI分析概述用戶如需對項目原理圖設計進行SI仿真分析。十堰了解PCB制板銷售PCB制板制作設計工藝流程。

PCB制板,完整稱為印刷電路板,是現代電子設備中不可或缺的重要組成部分。隨著科技的飛速發展,PCB制板的技術也日新月異,它不僅承載著電子元件,還為電路的連接提供了重要的平臺。它的制作過程復雜而精細,涉及多種先進技術的應用。從設計電路圖到**終成品,每一個環節都需要經過嚴格的把控,確保電路板的功能可靠性和安全性。在PCB設計的初期,工程師們通過專業軟件繪制出電路圖,精確計算每一個電路元件的布局和連接。他們需考慮到電流的流向、信號傳輸的路徑,以及電磁干擾等因素,這些都會直接影響到設備的性能。接下來,設計圖被轉化為實際的制作方案,印刷電路板的材料選擇尤為重要,常見的有玻璃纖維、聚酰亞胺等,它們各自擁有獨特的電氣性能和機械強度。

首先,PCB設計的第一步便是進行合理的電路設計與方案規劃。這一階段,設計師需要對整個系統的電子元器件進行深入分析與篩選,明確各個元器件的功能與工作原理,并根據電氣特性合理安排其布局。布局設計的合理性,直接關系到信號傳輸的效率及系統的整體性能。因此,在規劃之初,設計師應充分考慮各個元器件之間的相對位置,盡量減少信號干擾、降低電磁兼容性問題,確保電路的穩定運行。其次,隨著科技的發展,PCB的材料選擇呈現出多樣化的趨勢。高頻電路、柔性電路等新興技術的應用使得設計師需要了解不同材料的特性,以便在使用時發揮其比較好性能。這就要求設計師必須熟悉各種PCB基材的優缺點,以及在特定應用場景下**合適的材料。合理選擇材料之后,還需要通過仿真軟件進行電路性能的模擬測試,以確保設計的可靠性與可行性。

PCB制板目前常見的制作工藝有哪些?

PCBA貼片生產過程中,由于操作失誤的影響,容易導致PCBA貼片的不良,如:空焊,短路,翹立,缺件,錫珠,翹腳,浮高,錯件,冷焊,反向,反白/反面,偏移,元件破損,少錫,多錫,金手指粘錫,溢膠等,需要對這些不良開展分析,并開展改進,提高產品品質。一、空焊紅膠特異性較弱;網板開孔不佳;銅鉑間距過大或大銅貼小元件;刮刀壓力大;元件平整度不佳(翹腳,變形)回焊爐預熱區升溫太快;PCB銅鉑太臟或是氧化;PCB板含有水分;機器貼片偏移;紅膠印刷偏移;機器夾板軌道松動導致貼片偏移;MARK點誤照導致元件打偏,導致空焊;二、短路網板與PCB板間距過大導致紅膠印刷過厚短路;元件貼片高度設置過低將紅膠擠壓導致短路;回焊爐升溫過快導致;元件貼片偏移導致;網板開孔不佳(厚度過厚,引腳開孔過長,開孔過大);紅膠沒法承受元件重量;網板或刮刀變形導致紅膠印刷過厚;紅膠特異性較強;空貼點位封貼膠紙卷起導致周邊元件紅膠印刷過厚;回流焊振動過大或不水平;三、翹立銅鉑兩邊大小不一造成拉力不勻;預熱升溫速率太快;機器貼片偏移;紅膠印刷厚度均;回焊爐內溫度分布不勻;紅膠印刷偏移;機器軌道夾板不緊導致貼片偏移;機器頭部晃動;紅膠特異性過強;爐溫設置不當。 隨著時代的發展,PCB制板技術也隨之提升。十堰了解PCB制板銷售

PCB制板的種類、柔性。十堰了解PCB制板銷售

在高速數字系統中,由于脈沖上升/下降時間通常在10到幾百p秒,當受到諸如內連、傳輸時延和電源噪聲等因素的影響,從而造成脈沖信號失真的現象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,可能由于很小的差異導致高速系統設計的失敗;在電子產品向高密和高速電路設計方向發展,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業界通常會采用在PCB制板前期,通過信號完整性分析工具盡可能將設計風險降,從而也促進了EDA設計工具的發展……信號完整性(SignalIntegrity,簡稱SI)問題是指高速數字電路中,脈沖形狀畸變而引發的信號失真問題,通常由傳輸線阻抗不匹配產生的問題。而影響阻抗匹配的因素包括信號源的架構、輸出阻抗(outputimpedance)、走線的特性阻抗、負載端的特性、走線的拓樸(topology)架構等。解決的方式可以采用端接(termination)與調整走線拓樸的策略。信號完整性問題通常不是由某個單一因素導致的,而是板級設計中多種因素共同作用的結果。信號完整性問題主要表現形式包括信號反射、信號振鈴、地彈、串擾等;1,AltiumDesigner信號完整性分析(機理、模型、功能)在AltiumDesigner設計環境下。十堰了解PCB制板銷售